Xtensa 调试器和跟踪器

The Perfect Solution for Debugging Xtensa Cores Across Diverse SoC Designs

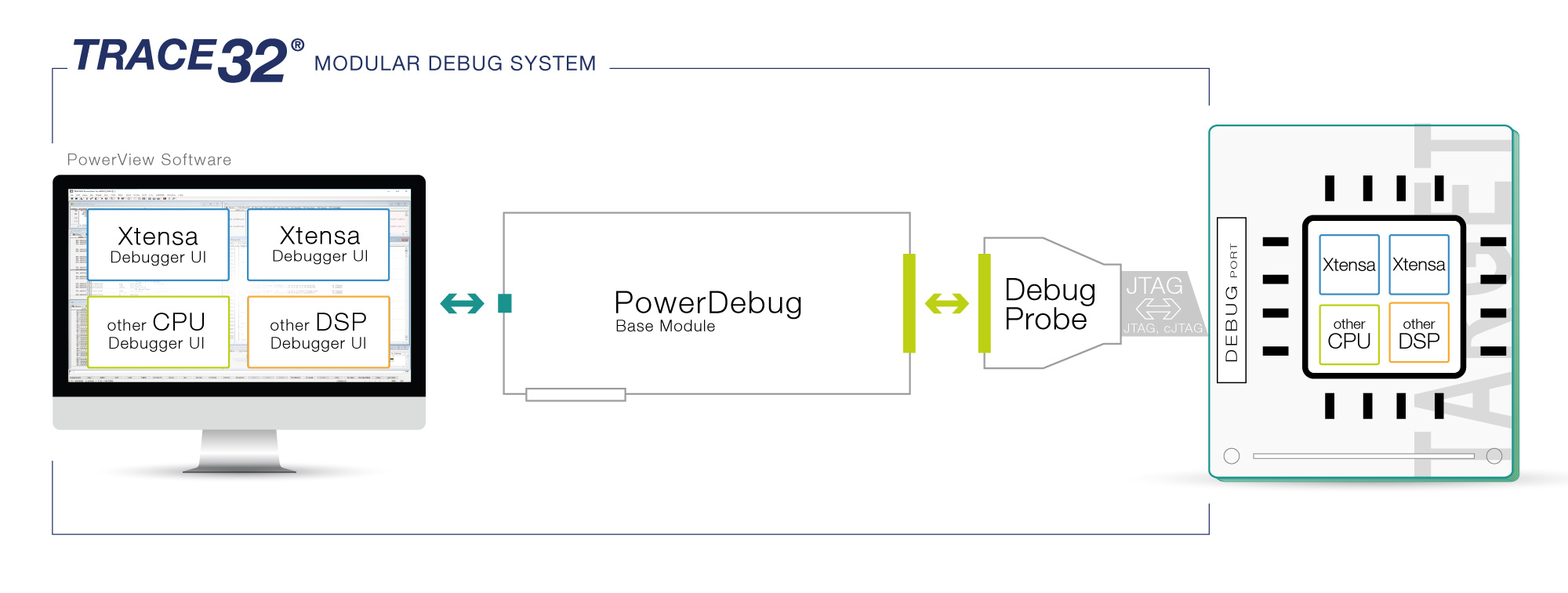

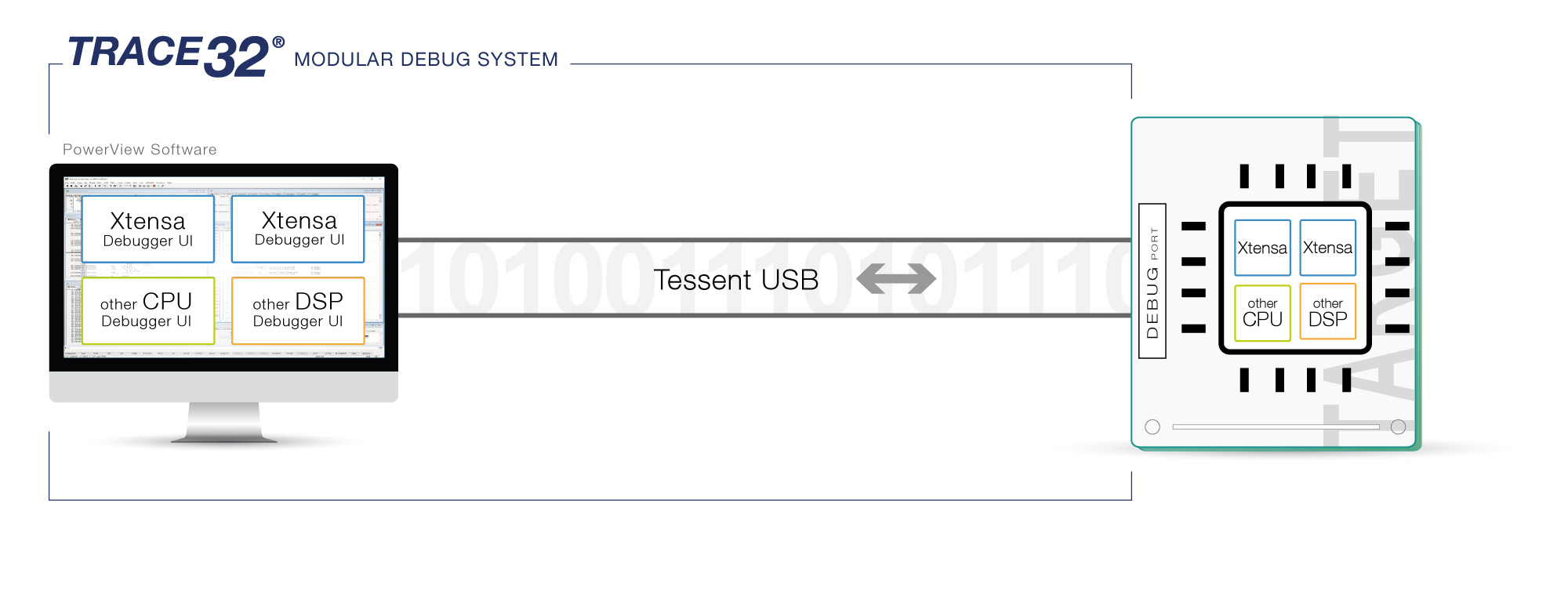

Xtensa是Cadence公司推出的可配置处理器IP,系统设计人员可以通过调整尺寸、选择功能和添加新指令来优化其嵌入式应用。使用我们世界领先的TRACE32®工具,您可以通过一个调试接口同时调试和控制SoC中的各种Xtensa内核(以及所有其他内核)。TRACE32® 支持所有级别的应用;从小型嵌入式控制器到大型多核计算密集型数据处理引擎。

支持的分区架构

Xtensa® LX4/LX5/LX6/LX7/LX8, Xtensa® NX

利用所有调试功能

Explore and utilize all the powerful and well-known features of your Xtensa core with Lauterbach debug modules: full on-chip breakpoint support; flash programming; benchmark counters; and cache view. And of course, everything is scriptable, enabling you to repeat the same test-sequence over and over.

进一步了解我们的调试系统

您想使用哪个 Xtensa 内核?

查看我们的预定义解决方案目录,找到适合您项目的理想工具集。

捕捉核心行动

Stop mode debugging can be a powerful tool but tracing is even better. Our Xtensa trace solutions support both the NEXUS-5001 compatible TRace Analyzer for Xtensa (TRAX) and off-chip tracing. TRAX is license free and stores the generated trace information to a user-configurable on-chip memory buffer. The off-chip trace solution provides significantly greater data gathering capabilities (up to 8GBytes) and support the embedding of TRAX packets in an Arm CoreSight trace stream. Used in the manner, trace correlation between cores can be performed.

*时间戳必须在 Xtensa 内核中配置。

您想使用哪个 Xtensa 内核?

查看我们的预定义解决方案目录,找到适合您项目的理想工具集。

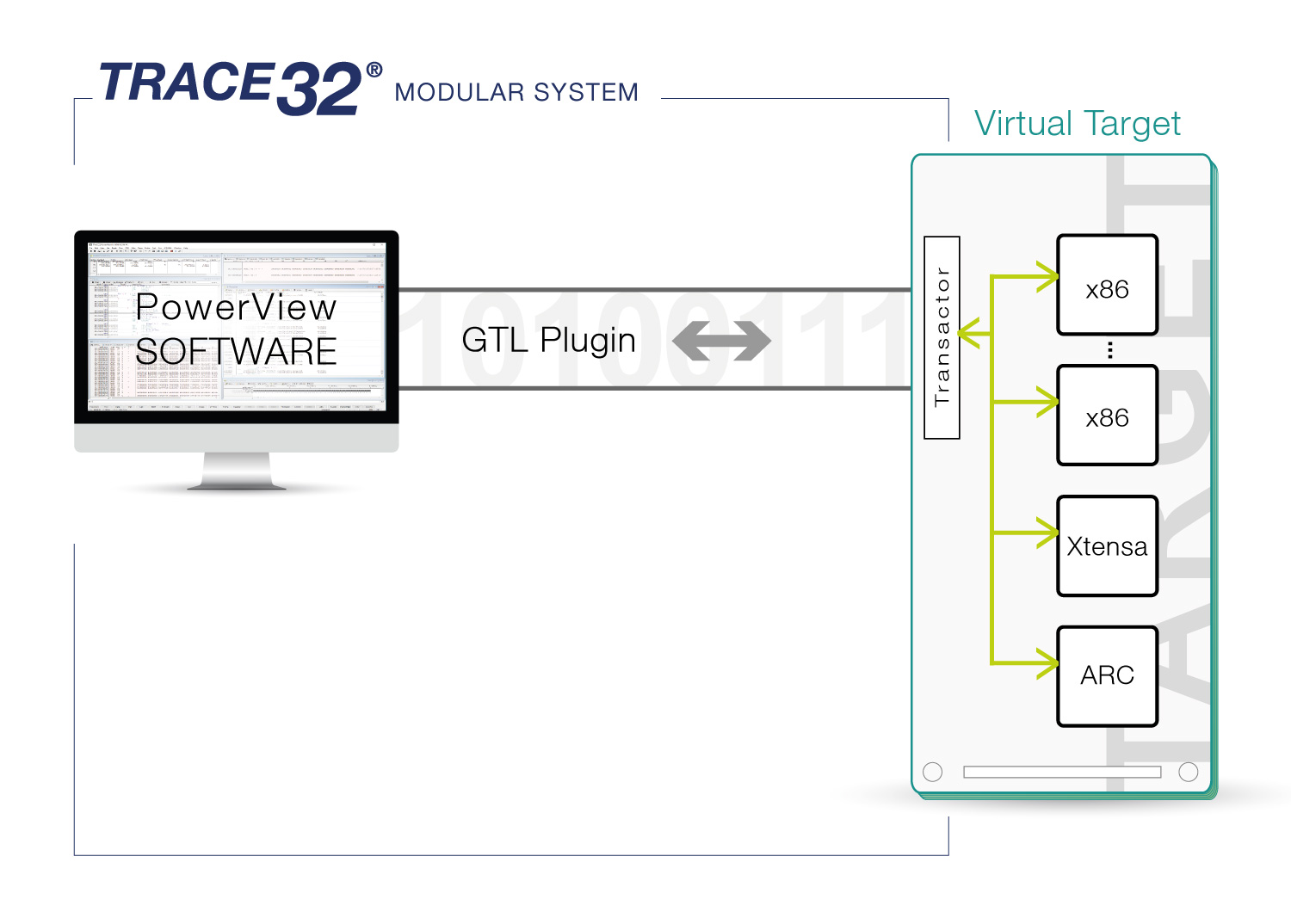

在您的硅之前做好准备

在 SoC 准备就绪之前,在定制 SoC 中测试 Xtensa 代码。测试 SoC 需要大量时间,但TRACE32 可以让你在虚拟原型和模拟器上开始软件开发,使用的图形用户界面和工具集与你以后在真正的芯片 上使用的相同。

使用仿真的 Verilog 或 VHDL 网表,在出厂前验证 SoC(包括调试机制)。劳特巴赫通用处理程序库(GTL)允许您在寄存器级执行硅前调试。