RISC-V® Debugger & Trace

任何 RISC-V 内核在任何芯片

利用我们领先的开发工具,分析任何实施 RISC-V 指令集架构 (ISA) 的设计,从使用 RV32 的单个微控制器到使用 RV64 的大型多核应用处理器。

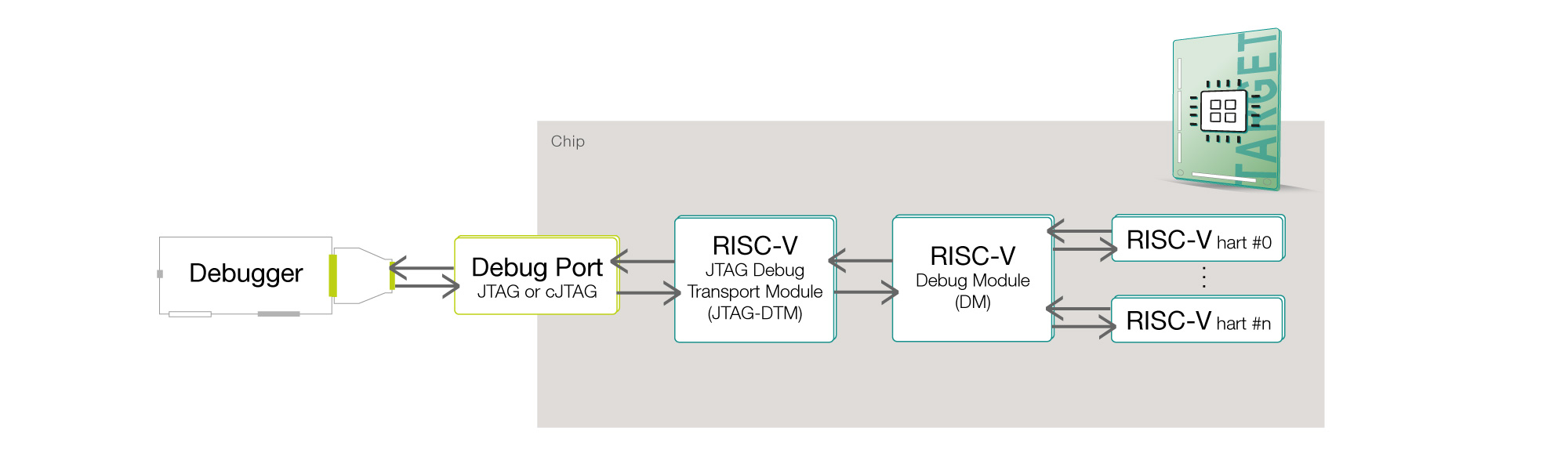

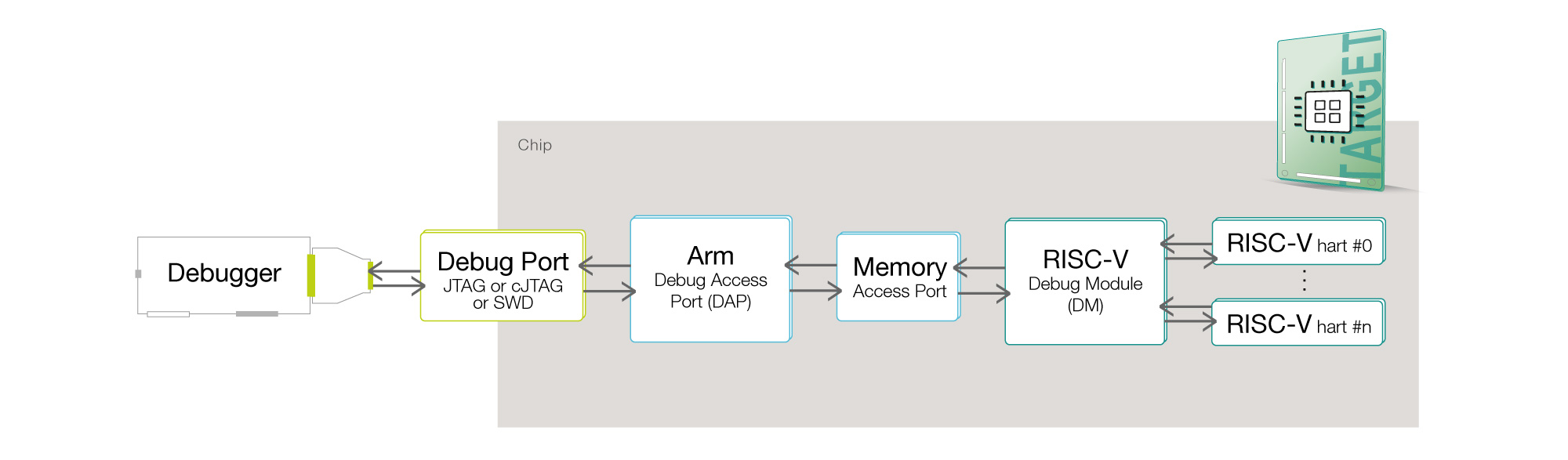

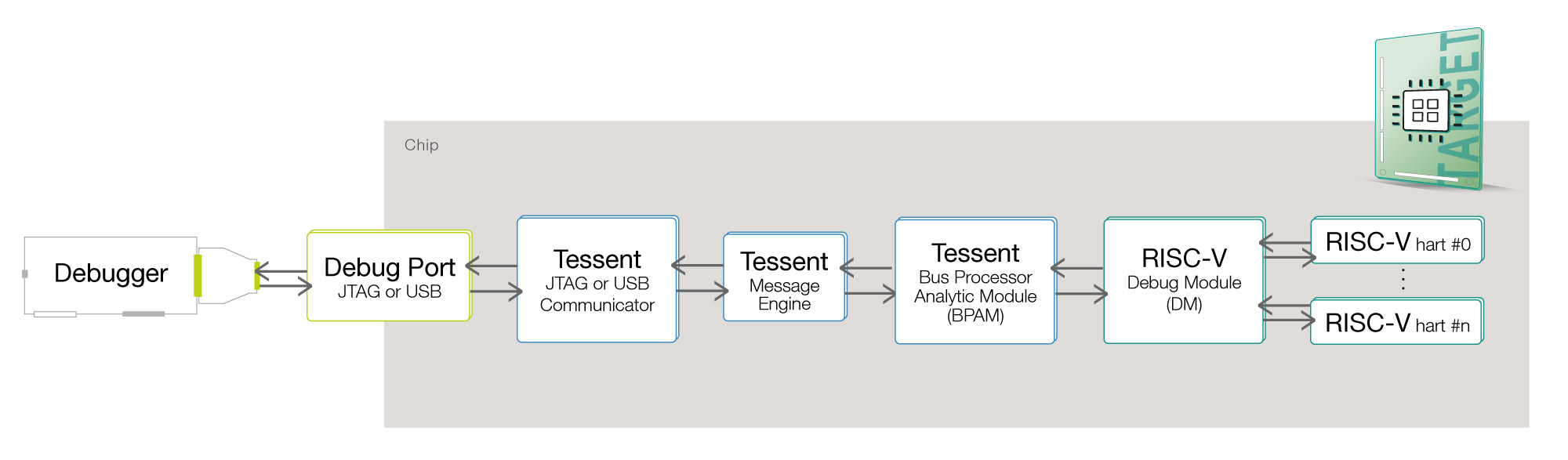

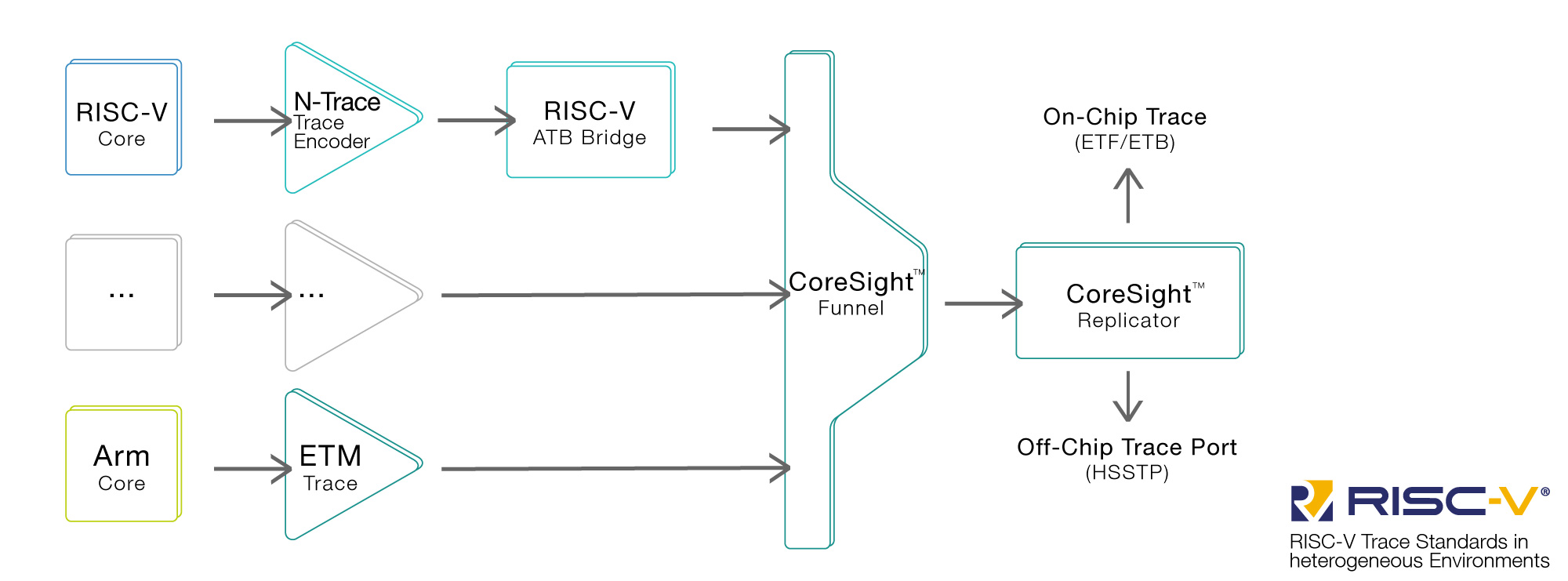

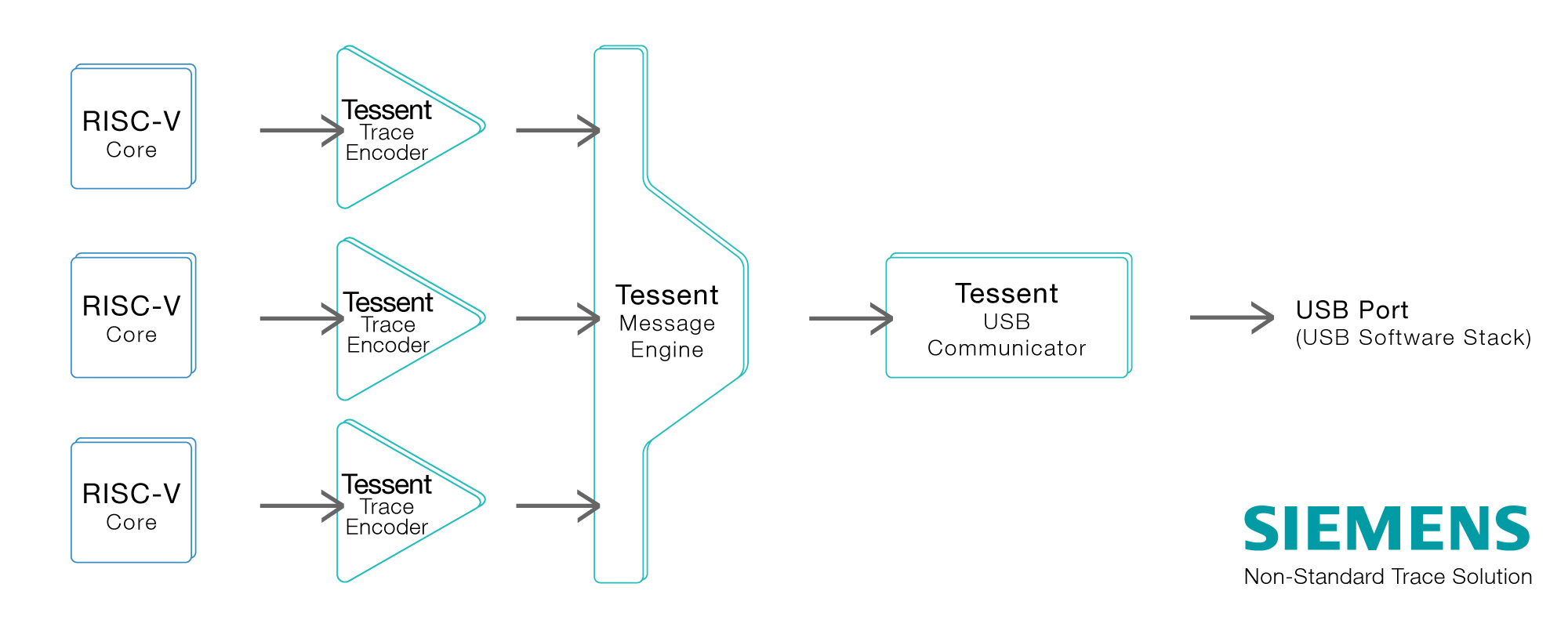

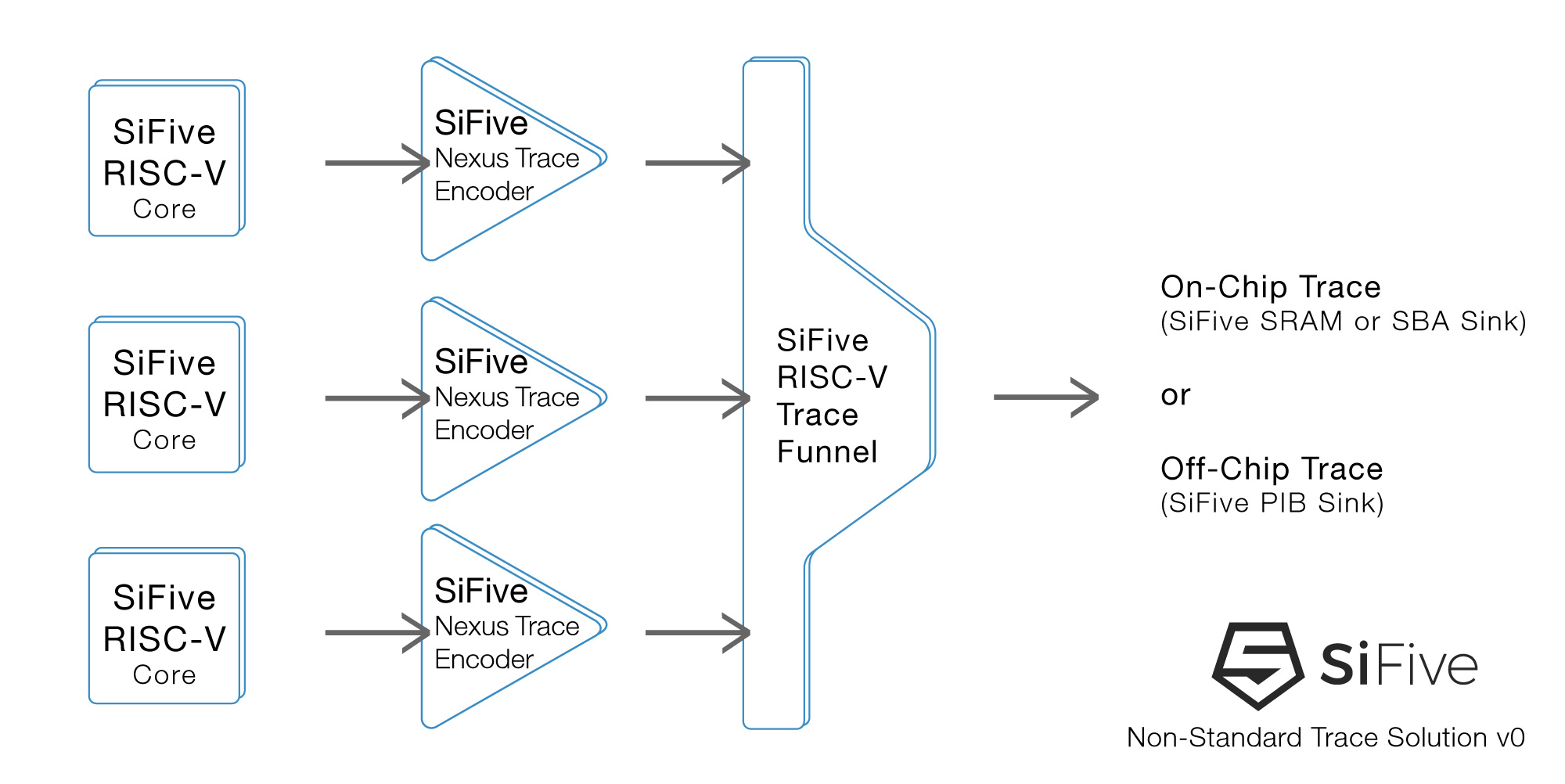

Using our TRACE32® tools you can debug and control any RISC-V core (along with all of the other cores) in any SoC via a single debug interface, all at the same time. TRACE32® tools support real-time on- and off-chip tracing for all major RISC-V trace systems.

从一开始,我们就是 RISC-V 基金会的战略成员,支持当今几乎所有采用 RISC-V ISA 的芯片 。得益于与 RISC-V 处理器设计者和半导体制造商的长期紧密合作,我们从一开始就支持未来芯片 的开发,确保您的投资面向未来。

支持的分区架构

RISC-V 32bit/64bit, AndesCore™ V5, ARC-V™, MicroBlaze™ V, Nios® V, SiFive® Core IP

利用所有 RISC-V ISA 扩展的所有调试功能

By using our powerful debug modules you can apply our full debug feature set to any RISC-V core design including all ISA extensions like floating point, compressed instructions, vector arithmetic, atomic instructions, integer multiplication and even custom ISA extensions. Utilize full on-chip breakpoint support, run-time memory access, flash programming and benchmark counters. Everything is scriptable, which enables you to automate tests very easily.

进一步了解我们的调试系统您想使用哪个 RISC-V 内核?

查看我们的预定义解决方案目录,找到适合您项目的理想工具集。

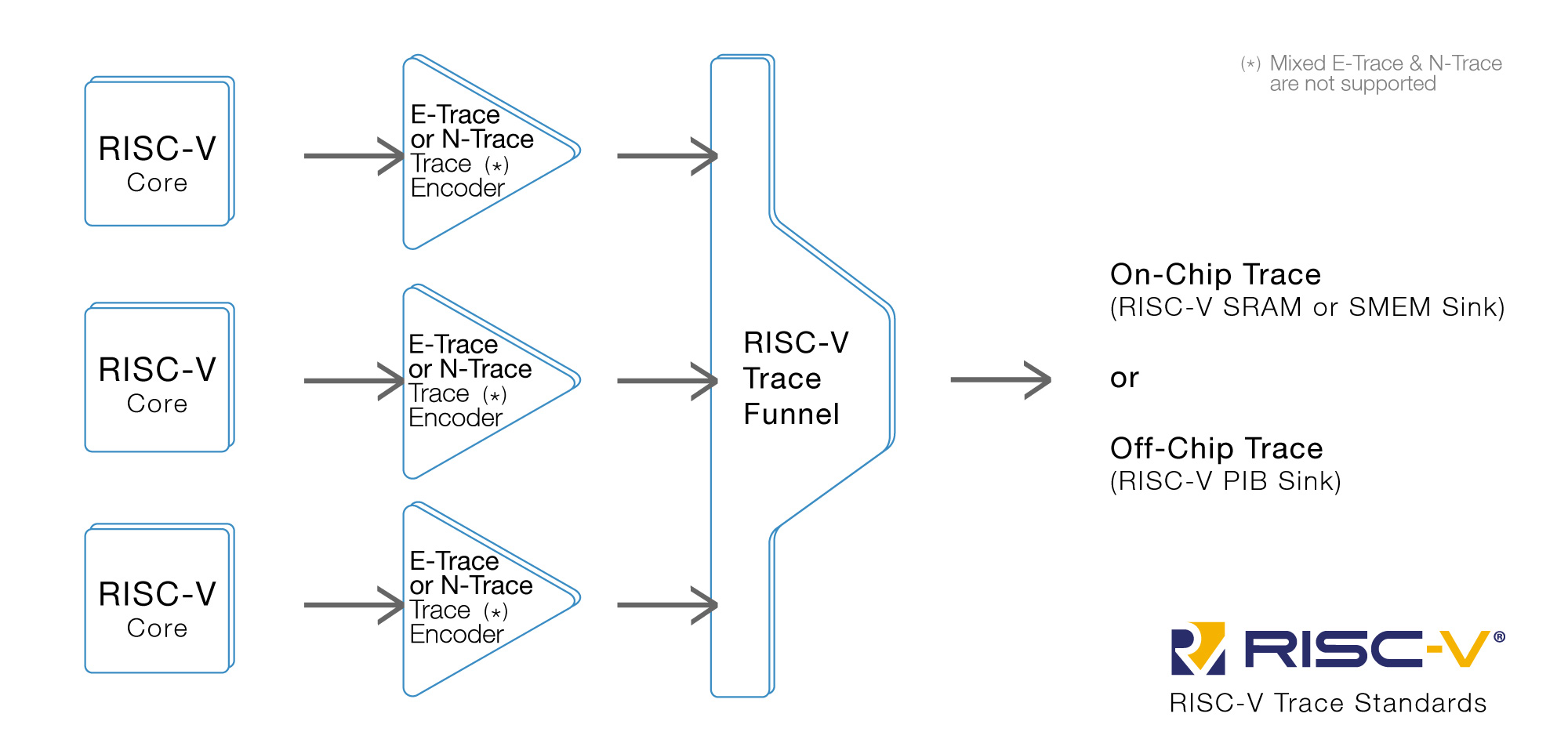

在每个 RISC-V 上捕捉您的核心操作芯片

Stop mode debugging can be a powerful tool but tracing is even better. Our trace solutions for RISC-V support both on-chip trace for various technologies as well as the much more powerful off-chip trace, which can save the trace data inside the target memory or emit it to one of our PowerTrace tools.

您想使用哪个 RISC-V 内核?

查看我们的预定义解决方案目录,找到适合您项目的理想工具集。

在您的硅之前做好准备

在 SoC 准备就绪之前,在定制 SoC 中测试 RISC-V 代码。测试您的 SoC 需要大量时间,但TRACE32 允许您在虚拟原型和模拟器上开始软件开发,使用的图形用户界面和工具集与您以后在真正的芯片 上使用的相同。在某种程度上,您也可以在开始编译之前验证单个 SoC 的调试接口。

支持 RISC-V 的第三方工具

TRACE32 支持的所有架构 都具有以下功能。如果此处未列出您的设备或工具,请与我们联系;支持通常已经在路上。